Syntacore RISC-V MCU IP 特性与概述

1. 引言

选择 RISC-V 处理器内核是一个关键步骤,需要全面评估多种因素,包括功能、性能、功耗、物理尺寸和软件兼容性。基于特定的应用需求,采用系统化且平衡的方法,可以确保获得满足技术和业务目标的最佳配置。

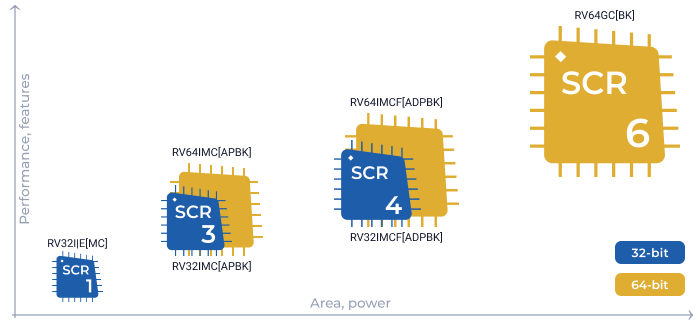

Syntacore 提供先进的 RISC-V 处理器 IP 组合,从适用于深度嵌入式应用的 32 位紧凑型 MCU 内核,到支持内存一致性、SMP 和 Linux 的高性能 64 位多核集群。本文详细概述了 Syntacore 更新的 RISC-V 微控制器内核——SCR1、SCR3、SCR4 和 SCR6。

本文旨在帮助工程师和 SoC 设计师:

- 了解 SCR 微控制器内核的技术特性。

- 评估性能、功耗、面积和功能之间的权衡。

- 在设计新设备时做出深思熟虑的决策。

2. 特性与应用

Syntacore 的微控制器级 IP 组合包含 4 款可配置、经过硅验证、面积优化的处理器内核:SCR1(32位)、SCR3(32/64位)、SCR4(32/64位)和 SCR6(64位)。这些内核专为各种 MCU 应用量身定制,范围涵盖紧凑型、高能效的嵌入式微控制器,到用于音频和图像处理的高性能系统。

图片1. Syntacore's MCU IP portfolio.

- SCR1 — 紧凑型入门级 32 位微控制器内核,采用 4 级顺序流水线。该内核针对最小面积(小于 15k 逻辑单元)进行了优化,并在 SHL 许可证下开源,允许商业使用。

- SCR3 — 高效的 32/64 位微控制器内核,支持多核、具备 DSP 能力、采用 5 级顺序流水线、包含内存保护单元(MPU)以及 L1 和 L2 缓存。

- SCR4 — 高效的 32/64 位微控制器内核,支持多核、具备 DSP 能力、采用 5 级顺序流水线、包含浮点单元(FPU)、内存保护单元(MPU)以及 L1 和 L2 缓存。

- SCR6 — 高性能 64 位微控制器内核,支持多核、采用 12 级乱序超标量流水线、包含高性能浮点单元(FPU)、物理内存保护(PMP)单元以及 L1 和 L2 缓存。

3. 选择 SCR 内核的架构与微架构标准

选择微控制器内核时,考虑其功能特性至关重要,例如位宽、指令集架构(ISA)、内存子系统、中断控制器和接口。最佳选择需要在足够的功能性和最小化系统资源消耗之间取得平衡。

3.1 核心特性

位宽

SCR 微控制器 IP 组合包含 32 位(SCR1、SCR3、SCR4)和 64 位(SCR3、SCR4、SCR6)实现,均完全符合 RISC-V 规范,使开发人员能够根据特定应用需求选择最合适的内核。

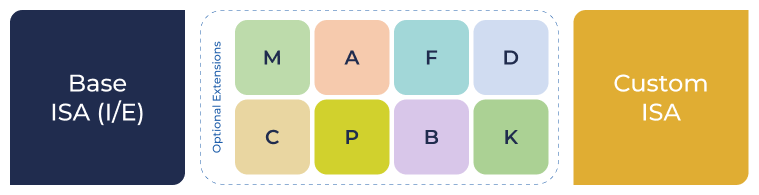

令集架构(ISA)

基本的 RISC-V 指令集(RV32I(E)/RV64I)是所有内核的必备项,它提供了基本的整数操作(算术、逻辑、内存访问、CSR 管理、分支等),足以应对简单的控制任务。然而,在为复杂应用设计 SoC 时,支持专门的 ISA 扩展(例如,位操作或加密)至关重要,能够更有效地执行目标计算工作负载。SCR MCU 内核支持的扩展完全符合官方 RISC-V 架构规范:

- SCR1 — RV32I|E[MC]* 包括乘除操作和压缩指令,确保最低的实现复杂度

- SCR3 — RV[32|64]IMC[APBK] 包括乘除操作、压缩指令以及 A、P、B、K 扩展(原子操作、打包 SIMD、位操作和加密功能)。

- SCR4 — RV[32|64]IMCF[ADPBK] 包括乘除操作、压缩指令、用于单精度和双精度浮点计算的 F 和 D 扩展,以及 A、P、B、K 扩展(原子操作、打包 SIMD、位操作和加密功能)。

- SCR6 — RV64GC[BK] 包括乘除操作、压缩指令、原子功能、用于单精度和双精度浮点计算的 F 和 D 扩展,以及 B、K 扩展(位操作和加密功能)。

*可选扩展在括号内表示。

扩展字母编码:I: 基础整数, E: 精简基础整数, M: 整数乘除, A: 原子指令, F: 单精度浮点, D: 双精度浮点, C: 压缩指令, P: 打包 SIMD, B: 位操作, K: 标量密码学, G: 通用扩展(包含 I、M、A、F、D 扩展)。

有关最新的、已批准的 RISC-V ISA 规范,请访问: https://riscv.org/technical/specifications

图片 2. RISC‑V architecture extensions.

流水线

流水线是处理器核心架构的关键要素,决定了其计算性能。SCR1、SCR3 和 SCR4 内核采用顺序流水线,强制按程序顺序顺序处理指令。SCR1 采用 2-4 级流水线,设计简单紧凑。SCR3 和 SCR4 采用更深的 3-5 级流水线,提高了执行并行度。

SCR6 实现乱序执行,可动态重排指令以优化计算单元利用率,并额外支持超标量架构,允许每个周期同时执行多条指令。该内核采用深流水线(10-12 级),提供了更高的吞吐量。

SMP

SCR 内核可作为嵌入式系统的独立解决方案有效运行,但也可以组合成集群以提高计算能力并执行更复杂的任务。SCR3、SCR4 和 SCR6 微处理器内核支持利用共享 L2 缓存的一致性多核配置,能够无缝集成不同的核心类型(例如,2xSCR3+2xSCR6)。集群最多可包含 8 个核心,提供了灵活性和可扩展性。

图片 3. Example of a heterogeneous cluster based on SCR cores (MCU + APU).

表 1. SCR 内核的关键架构和微架构特性

| 核心特性 | SCR1 | SCR3 | SCR4 | SCR6 |

|---|---|---|---|---|

| ISA | RV32I|E[MC] | RV[32|64]IMC[APBK] | RV[32|64]IMCF[ADPBK] | RV64GC[BK] |

| 流水线类型 | 顺序 | 乱序,超标量 | ||

| 流水线级数 | 2‑4 级 | 3‑5 级 | 10‑12 级 | |

| SMP 支持 | – | 可选,最多 4 核,一致性 | 可选,最多 8 核,一致性 | |

3.2 内存子系统

缓存和 TCM

SCR MCU 内核配备了可扩展的内存子系统,包括可配置大小的 TCM、具有一致性和错误保护功能的 L1 和 L2 缓存。11

SCR1 支持基本配置,最高 64KB TCM 内存,确保了对实时应用至关重要的快速访问时间。

SCR3、SCR4 和 SCR6 内核提供增强的内存子系统功能:

- SCR3/4/6 - TCM 最高 256 KB,带奇偶校验/ECC 保护;

- 缓存:

- SCR3/4 - L1:最高 32+32 KB(指令/数据),带奇偶校验/ECC 保护;L2:128-512 KB,带 ECC;

- SCR6 - L1:最高 64+64 KB,带奇偶校验/ECC 保护;L2:128 KB - 2 MB,带 ECC;

- 硬件缓存一致性

- 集成到基于 L3 的集群(带 CHI 接口)

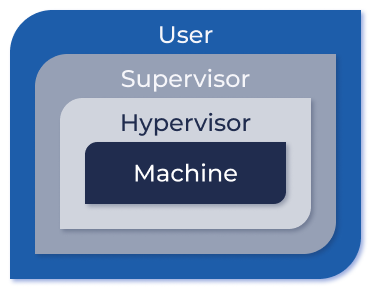

特权级别

RISC-V 规范定义了一种基于特权和非特权模式的分层多级内存访问方案,范围从负责核心系统功能和 OS 内核管理的最低级机器模式(M),到在运行 Linux 的应用类处理器中实现任务虚拟化和安全执行的超级监视器级别(H)。

图片 4. Privilege levels in the RISC‑V architecture.

SCR MCU 内核提供强大的隔离和特权模式分离,SCR1 内核在机器(M)级别提供分离,而 SCR3、SCR4 和 SCR6 内核额外支持用户(U)模式,可在裸机或实时操作系统(RTOS)中灵活部署敏感应用。硬件内存保护通过 SCR3 和 SCR4 内核中的 MPU(支持最多 32 个区域)以及 SCR6 内核中的 PMP 模块(能够管理最多 64 个区域)来强制执行。

表 2. SCR MCU 内存子系统规格

| 特性 | SCR1 | SCR3 | SCR4 | SCR6 |

|---|---|---|---|---|

| 执行级别 | M‑mode | U, M- modes | ||

| TCM | 最高 64KB | 可选,最高 256KB 奇偶校验/ECC | ||

| L1 缓存 | – | 可选,最高 64KB(I+D),奇偶校验/ECC | 最高 128KB(I+D),奇偶校验/ECC,支持步长数据预取器 | |

| L2 缓存 | – | 可选,128KB 至 512KB,ECC | 128KB 至 2MB,ECC | |

| 内存保护 | – | MPU,最多 32 个区域 | PMP,最多 64 个区域 | |

3.3 接口、调试与中断

接口与调试

SoC 需要高水平的组件集成、快速的数据传输能力和可扩展性以满足性能要求。此外,调试接口的可用性至关重要,能够实现及时的错误检测和恢复,显著提高整个系统的可靠性、稳定性和质量。

SCR1 内核使用标准的 32 位数据传输 AXI/AHB-Lite 总线,并具有 JTAG 或 cJTAG* 调试接口。SCR3 和 SCR4 支持 AHB/AXI 数据总线(最高 128 位宽)、JTAG/cJTAG 调试接口、用于直接内存访问的 TCM AXI 从端口以及用于外部加速器集成的 L2 AXI 一致性端口。SCR6 支持最高 256 位的 AXI 数据宽度,确保高性能并支持带缓存内存的复杂系统,具有 JTAG 或 cJTAG* 兼容调试接口、TCM AXI 从端口和 L2 AXI/ACE 一致性端口,确保系统可扩展性。

*可根据要求提供

中断系统

SCR 内核中的中断控制器提供了处理各种中断类型的广泛能力,能够高效处理不同复杂度和专业性的任务。SCR 内核支持以下类型的中断控制器:

核心级中断控制器:

- IPIC(可编程中断接口控制器) 一种本地中断控制器(最多支持 32 个中断线和 32 个优先级(基于中断 ID))。提供最小延迟,支持向量中断以及 M 和 S 模式。

- CLIC(核心本地中断控制器) 本地中断控制器(16 个内部中断和最多 4080 个外部中断线)支持可编程优先级(最多 256 级)、向量中断以及 M 和 S 模式。提供为每个中断配置不同模式的灵活性。

平台级中断控制器:

- PLIC/ACLINT

- PLIC — 集群级中断控制器,聚合外围设备的中断并将其路由到核心。提供可扩展性,支持最多 1023 个中断线和最多 256 个优先级。

- ACLINT — 处理器间中断控制器,生成系统定时器中断(MTIME/MTIMECMP)、软件中断(Machine Software Interrupt (MSWI) 和 Supervisor Software Interrupt (SSWI)),支持最多 4096 个中断线。

- AIA(高级中断架构)- APLIC+IMSIC*

- APLIC(高级平台级中断控制器) 是集群级控制器,具有高级中断路由和管理功能,并支持 MSI(消息信号中断)。它支持最多 1023 个中断线和每个硬件线程(hart)最多 2047 个唯一中断标识符、动态路由和可编程优先级,可在复杂系统中实现灵活的中断分发。

- IMSIC(传入消息信号中断控制器) 是集成到 APLIC 中的中断控制器。它通过专用寄存器将中断映射到内存,无需传统的硬连线 IRQ 线。它使用 MSI 消息进行信令,中断作为写入紧凑的 4-KiB 内存页传递,并立即馈送到 M/S 级别。

SCR1 内核支持基于 IPIC 控制器的基本中断系统,能够处理最多 16 个中断线,支持最多 16 个优先级。

SCR3 和 SCR4 内核提供高级中断支持:现代 CLIC 控制器管理最多 4096 个中断线和 256 个优先级;能够处理 1023 个中断、具有 256 个优先级的 PLIC;以及支持最多 4096 个中断线(包括机器模式下的定时器中断和机器/监管者模式下的软件中断)的 ACLINT 控制器。

SCR6 内核采用先进的中断架构,结合了与 SCR3/4 类似的 PLIC(支持最多 1023 条中断线和 256 个优先级)以及由 APLIC 和 IMSIC 控制器组成的创新 AIA 系统。这种集成能够处理最多 1023 个中断线,并支持 2047 个唯一标识符,这显著扩展了系统在高性能场景下的能力。

*可根据要求提供

表 3. SCR 内核接口和中断控制器概述

| 功能/核心 | SCR1 | SCR3 和 SCR4 | SCR6 | |

|---|---|---|---|---|

| 中断控制器 | IPIC | 最多 16 个中断线,最多 16 个优先级(基于中断 ID) | – | – |

| CLIC | – | 最多 4096 个 IRQ,最多 256 个优先级 | – | |

| PLIC/ACLINT | – | 最多 1023/4096 个 IRQ,最多 256 个优先级 | ||

| AIA (APLIC + IMSIC)* | – | – | 每个 hart 最多 1023 个中断线,最多 2047 个不同中断标识 | |

| 总线接口 | AXI 32 位数据 | AXI 32/128 位数据或可选从端口 | 可缓存 AXI 64/128/256 位数据 | |

| AHB-Lite 32 位数据 | AHB 32/128 位数据 | 可选非可缓存 AXI 64/128/256 位数据 | ||

| 调试接口 | JTAG 或 cJTAG* | |||

| 可选外部端口 | – | TCM AXI 从端口 | ||

| 可选一致性接口 | – | AXI L2 缓存一致性端口 | AXI/ACE L2 缓存一致性端口 | |

*可根据要求提供

下表总结了 SCR MCU 内核,展示了其关键规格和显著特性。

表 4. SCR MCU 内核关键特性总结

| 特性 | SCR1 | SCR3 | SCR4 | SCR6 |

|---|---|---|---|---|

| ISA | RV32I|E[MC] | RV[32|64]IMC[APBK] | RV[32|64]IMCF[ADPBK] | RV64GC[BK] |

| 流水线类型 | 顺序 | 乱序,超标量 | ||

| 流水线级数 | 2‑4 级 | 3‑5 级 | 10‑12 级 | |

| 执行级别 | M‑mode | U, M- modes | ||

| SMP 支持 | – | 可选,最多 4 核,一致性 | 可选,最多 8 核,一致性 | |

| FPU | – | – | 单精度和双精度 | 高性能,单精度和双精度 |

| TCM | 最高 64KB | 可选,最高 256KB 奇偶校验/ECC | ||

| L1 缓存 | – | 可选,最高 64KB(I+D),奇偶校验/ECC | 最高 128KB(I+D),奇偶校验/ECC,支持步长数据预取器 | |

| L2 缓存 | – | 可选,128KB 至 512KB,ECC | 128KB 至 2MB,ECC | |

| 内存保护 | – | MPU,最多 32 个区域 | PMP,最多 64 个区域 | |

| 中断控制器 | IPIC-最多 16 个中断线,最多 16 个优先级(基于中断 ID) | CLIC-最多 4096 个 IRQ,最多 256 个优先级 | – | |

| PLIC/ACLINT-最多 1023/4096 个 IRQ,最多 256 个优先级 | ||||

| – | AIA(APLIC+IMSIC)* 最多 1023 个中断线,每个 hart 最多 2047 个不同中断标识 | |||

| 接口选项 | AXI, AHB‑Lite | AXI, AHB | AXI, ACE | |

| 调试接口 | JTAG 或 cJTAG* | |||

| 目标市场 | IoT, 智能家居, 控制系统 | 工业, IoT, 智能家居 | 工业, IoT, 移动设备 | 工业, 传感器融合, 图像和音频处理 |

*可根据要求提供

4. 选择 MCU SCR 内核的 PPA 标准

我们之前讨论了 SCR 内核的功能特性,这是选择过程中必要但初步的步骤,可确保内核功能与所开发 SoC 的要求保持一致。考虑到流片的高成本和错误的严重影响,在设计过程早期了解内核的物理参数——功耗(P)、性能(P)和面积(A)——至关重要。PPA(功耗、性能、面积)分析用于评估和优化这些参数。

4.1 性能

频率、性能和功耗是相互依存的要素,共同决定了最终产品的特性。在实践中,必须在这些参数之间找到折衷方案,因为最大化某个参数可能会显著降低其他参数,从而破坏平衡。表5显示了通过综合基准测试和核心时钟频率获得的性能值。这些测量结果并非最终数据,仅供参考。

表 5. MCU SCR 性能与频率

| 参数/核心 | SCR1 | SCR3 (RV32/RV64) | SCR4 (RV32/RV64) | SCR6 |

|---|---|---|---|---|

| Dhrystone, per/MHz 最优 (LTO) | 3,15 | 4,40/5,70 | 4,35/5,70 | 10,40 |

| Coremark, per/MHz 最优 | 3,05 | 3,72/3,68 | 3,66/3,69 | 6,35 |

| 频率, MHz (28 HPC+) | 1200+ | 1200+ | 1200+ | 1400+ |

注 1:编译条件

- Coremark: LLVM‑20 ‑mcpu=scrX ‑O3 ‑funroll‑loops ‑finline‑functions ‑mllvm ‑‑enable‑dfa‑jump‑thread ‑falign‑functions=8 ‑falign-loops=4 ‑mllvm ‑scr‑loop‑streaming ‑mllvm ‑‑crc‑matcher=true ‑mllvm -enable-loop-int-wrap-predication=true

- Dhrystone: LLVM‑20 ‑ ‑mcpu=scrX ‑O3 ‑falign‑functions=8 ‑falign‑loops=4 ‑mllvm ‑riscv-enable-gep-opt=true ‑flto

注 2:频率测量条件

- Dhrystone 2.1_02, BM from TCM/L1

- LVT, Typical, 25C, 28HPC+

注3:SCR1 配置 - RV32IM, 3 级流水线, TCM 32KB

4.2 面积与功耗

除了性能之外,面积和功耗也是同等重要的参数。面积相关数据是一个复杂的问题,取决于许多因素,包括内存容量、IP 核配置和测量条件。为便于理解,我们仅提供最常见 28 HPC 工艺下核心逻辑的数据。这些是近似值,对于每个具体任务,我们的技术专家随时准备根据内核的技术能力帮助满足任何(合理的)目标。

表 6. MCU SCR 面积与功耗

| 参数 | 描述 | SCR1 | SCR3 (RV32/RV64) | SCR4 (RV32/RV64) | SCR6 |

|---|---|---|---|---|---|

| 面积, kGates | 核心逻辑,起始值 | 10 | 50/75 | 95/115 | 400 |

| 面积, mm2 | 核心逻辑,起始值 | 0,004 | 0,016 | 0,026 | 0,10 |

| 功耗, uW/MHz | 动态(核心逻辑),起始值 | 1,40 | 2,73 | 3,00 | 13,20 |

注 4:面积和功耗测量条件

- 面积:LVT@100MHz for 28HPC, 无 DFT

- 功耗:在后物理综合门级网表上测量,Dhrystone 2.1_02, 500 次运行的最后 10 次迭代, HVT, TYP@100MHz for 28HPC

SCR1 以其卓越的性能、紧凑尺寸和低功耗组合,非常适合简单的嵌入式应用,包括物联网、工业和消费类设备。

SCR3 和 SCR4 提供更高的性能指标、扩展的功能集——最多 5 级流水线、支持 DSP 操作、浮点功能(仅 SCR4)以及紧凑的尺寸,使其适用于更复杂的计算任务,包括智能家居、物联网和工业应用。

SCR6 在 Syntacore 的 MCU 产品组合中提供最高性能。这是通过超标量架构、12 级双发射流水线、支持高性能 FPU 以及丰富的内存子系统实现的,使其非常适合高负载任务,包括工业自动化、图像和语音处理、汽车、传感器融合、智能家居和智慧城市应用。同样值得注意的是,其更深的流水线支持更高的时钟速率,而与较长流水线相关的性能损失被所使用的先进架构和微架构解决方案所抵消。

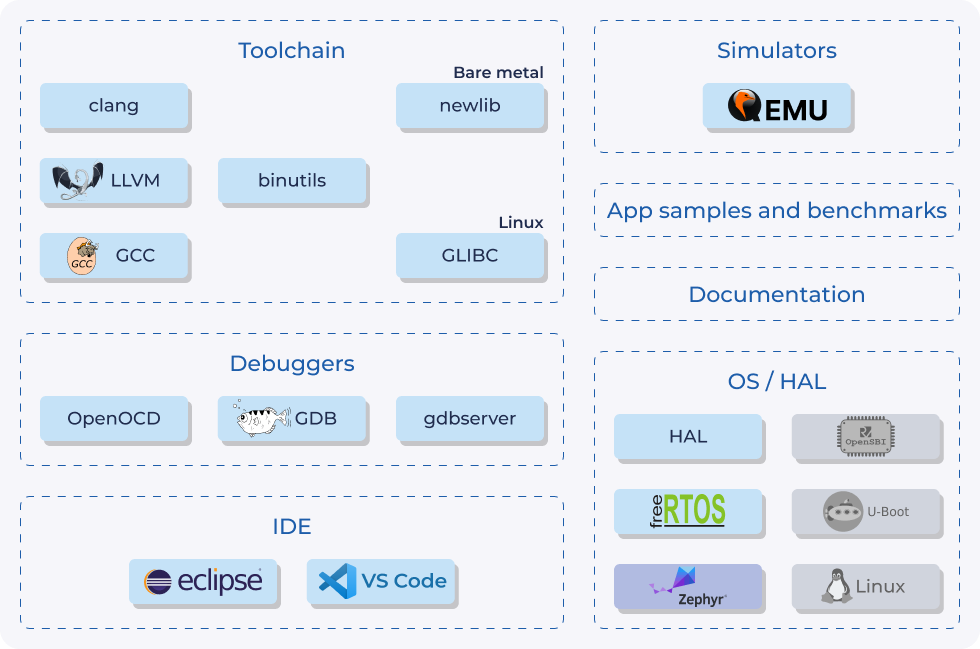

5. 完整的开发平台、定期更新与支持

之前,我们讨论了 SCR 内核的硬件组件及其微架构特性。然而,硬件不能孤立运行——还需要全面的软件支持。重要的不仅仅是一套软件工具,而是一个完整的套件,使工程师能够快速轻松地启动项目,最大限度地减少人力成本并加速实施过程。

Syntacore 为 SCR 内核提供了一个全面的软件平台,具有基于现代工具链的预配置 IDE、调试工具、功能模拟器和引导加载程序,所有组件都集成到一个统一的软件包中。该解决方案为整个开发周期(从初始原型设计到最终设备调试)提供端到端支持,通过所有组件的优化集成和与 SCR 处理器系列的保证兼容性,显著加快产品上市时间。软件包的所有组件都会定期更新,确保可以访问最新版本。Syntacore 还提供跨整个软件范围的持续支持和专业咨询,确保有效解决出现的任何问题。

Syntacore 软件包括:

- 专业软件开发套件(预构建的 GCC 和微架构优化的 clang/LLVM 工具链、预配置的 Eclipse 和 Visual Studio Code IDE、QEMU 模拟环境、BSP、调试工具和库)

- 基本系统软件(一系列经过 SCR 内核测试的 RISC-V 兼容工具和系统软件:预配置的 Linux*、Zephyr、FreeRTOS 操作系统、引导加载程序、运行时等)

- 全功能 FPGA SDK(基于领先供应商的 FPGA 开发板,支持多种 JTAG/cJTAG 适配器)

*仅适用于 APU 级 SCR 内核(SCR5、SCR7 和 SCR9)

图片 5. SC‑DT package contents (Zephyr OS is downloaded separately).

OpenSBI, U‑Boot, and Linux are applicable only to APU‑class SCR cores

6. 总结

选择处理器内核是一个复杂、多步骤的过程,需要细致分析待解决的应用任务,并根据这些要求仔细选择计算功能。

本文深入分析了 SCR 微控制器内核,涵盖了位宽、指令集、流水线架构、内存子系统、中断控制器和支持的接口等基本特性。还探讨了核心选择的关键标准,包括基准测试结果、面积和功耗,从而能够为各种应用更明智地确定最佳解决方案。

Syntacore 更新的 SCR MCU 内核组合提供了全面的 IP 选择,从紧凑、高能效的解决方案到完全符合 RISC-V 架构的高性能处理器。每个内核都旨在满足应用需求,在性能、效率和可扩展性之间提供最佳平衡:

- SCR1 适用于物联网、智能家居和控制系统中需要最小面积和功耗的紧凑型嵌入式系统。

- SCR3 为物联网和工业控制器提供平衡的性能,支持裸机和 RTOS 操作系统。

- SCR4 带有浮点支持,专为工业物联网和移动应用中的高性能任务而设计。

- SCR6 凭借其超标量流水线,专为需要高计算能力的任务而设计,例如复杂嵌入式应用中的图像和音频处理、网络处理器和传感器融合。